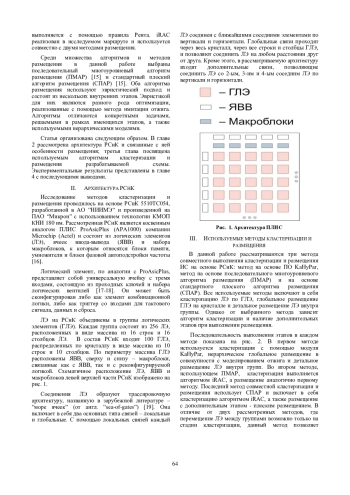

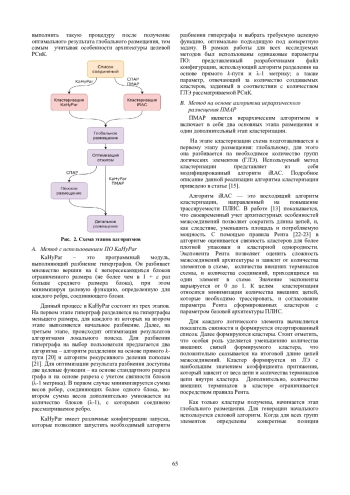

Реконфигурируемые системы на кристалле (РСнК) занимают все большую долю на рынке микро- и наноэлектроники. Наличие программируемой части в совокупности с жесткими сложными функциональными (СФ) блоками на одном кристалле делает их универсальными и пригодными для выполнения разного рода задач. При проектировании интегральных схем (ИС) на основе РСнК остро стоит вопрос быстродействия схем. Оно зависит как и от архитектуры целевой реконфигурируемой системы, так и от результатов каждого этапа маршрута проектирования. Основополагающим фактором, влияющим на скорость распространения сигнала между логическими элементами, является их расположение относительно друг друга. Это определяется на этапе кластеризации и размещения элементов разрабатываемой схемы на базе РСнК. В данной статье эти два этапа рассматриваются совместно, т. к. они неразрывно связаны друг с другом и решают общую задачу распределения логических элементов схемы по группам логических элементов РСнК. Для выполнения кластеризации и размещения выбраны методы, использующие программный модуль KaHyPar, последовательный многоуровневый алгоритм размещения (ПМАР) и стандартный плоский алгоритм размещения (СПАР). Результатом работы является сравнительный анализ представленных методов. В качестве оценки используются такие параметры как количество трассировочных элементов в цепях, количество цепей с определенным числом трассировочных элементов, а также трассируемость схем. На основе полученных результатов показаны преимущества и недостатки представленных методов.

Идентификаторы и классификаторы

В маршруте автоматизированного проектирования интегральных схем (ИС) на основе реконфигурируемых систем на кристалле (РСнК) и программируемых логических интегральных схемах (ПЛИС) все этапы неразрывно связаны друг с другом. Нельзя обособленно рассматривать конкретный этап маршрута, так как его влияние на другие этапы может быть значительным. Примером этого является взаимосвязь этапов кластеризации и размещения. Кластеризация представляет собой деление списка соединений разрабатываемой схемы на группы логических элементов (ГЛЭ). Размещение элементов выполняется на основе полученного разбиения и представляет собой перемещение ГЛЭ, перемещение ЛЭ внутри этих групп и легализацию их позиций. Эти два этапа могут быть выполнены как по отдельности, так и совокупности друг с другом. От результата кластеризации в дальнейшем зависит качество размещения, и, как следствие, трассируемость разрабатываемой схемы [1].

Если у вас возникли вопросы или появились предложения по содержанию статьи, пожалуйста, направляйте их в рамках данной темы.

Список литературы

1. Заплетина М.А., Железников Д.А., Гаврилов С.В. Иерархический подход к трассировке реконфигурируемой системы на кристалле островного типа // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2020. Выпуск 3. С. 1621. DOI: 10.31114/2078-7707-2020-3-16-21 EDN: OWJEMO

2. Miettinen P., Honkala M., Roos J. Using METIS and hMETIS Algorithms in Circuit Partitioning // Report CT-49, Circuit Theory Laboratory, Helsinki University of Technology, 2006.

3. Qatalyurek U., Aykanat C. PaToH (Partitioning Tool for Hypergraphs) // Encyclopedia of Parallel Computing, 2020. Springer US, Boston, MA, pp. 1479-1487. DOI: 10.1007/978-0-387-09766-4_93

4. Devine K. D., Boman E.G., Riesen L.A., Catalyurek U.V., Chevalier C. Getting started with zoltan: A short tutorial. // In Combinatorial Scientific Computing №09061 in Dagstuhl Seminar Proceedings, 2009, p. 10.

5. Vastenhouw B., Bisseling R. A Two-Dimensional Data Distribution Method For Parallel Sparse Matrix-Vector Multiplication // SIAM Review, 47, No. 1, 2005 pp. 67-95. DOI: 10.1137/S0036144502409019

6. Kim M. C., Lee D., Markov I. SimPL: An effective placement algorithm // IEEE TCAD, vol. 31, no. 1, 2012, pp. 50-60.

7. Gort M., Anderson J. H. Analytical placement for heterogeneous FPGAs // 22nd International Conference on Field Programmable Logic and Applications (FPL), 2012, pp. 143-150. DOI: 10.1109/FPL.2012.6339278

8. Hutton M., Adibsamii K. Leaver. A. Adaptive delay estimation for partitioning-driven PLD placement // IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 11, no. 1, pp. 60-63, Feb. 2003. DOI: 10.1109/TVLSI.2002.808424

9. Rose J., Snelgrove W., Vranesic Z. ALTOR: An automatic standard cell layout program // Proceedings of the Canadian Conference on VLSI, 1985, pp. 169 - 173.

10. Betz V., Rose J. VPR: A new packing, placement and routing tool for FPGA research // Proceedings of the 7th International Workshop on Field-Programmable Logic and Applications, ser. fPl ‘97. 1997, pp. 213-222. DOI: 10.1007/3-540-63465-7_226

11. Лебедев Б. К., Степаненко С. А. Генетический алгоритм размещения, управляемый временными ограничениями // Известия ЮФУ. Технические науки. 2007. №1. EDN: KNPWGD

12. Schlag S., Heuer T., Gottesburen L., Akhremtsev Y., Schulz C., Sanders P. High-Quality Hypergraph Partitioning // ACM J. Exp. Algorithmics Just Accepted, Association for Computing Machinery, New York, 2022. DOI: 10.1145/3529090 EDN: RUXUYM

13. Singh A., Parthasarathy G., Marek-Sadowska, M. Efficient circuit clustering for area and power reduction in FPGAs // ACM Trans. Design Autom. Electr. Syst. vol. 7, №4, pp. 643-663. DOI: 10.1145/605440.605448

14. Гаврилов С. В., Железников Д. А., Чочаев Р. Ж., Хватов В. М., Алгоритм декомпозиции на основе метода имитации отжига для реконфигурируемых систем на кристалле // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). 2018. № 1. С. 199-204. DOI: 10.31114/2078-7707-2018-1-199-204 EDN: YAEZML

15. Гаврилов С. В., Железников Д. А., Чочаев Р. Ж. Разработка и сравнительный анализ методов решения задачи размещения для реконфигурируемых систем на кристалле // Известия высших учебных заведений. Электроника. - 2020. - Т. 25., № 1, С. 48-57.,. DOI: 10.24151/1561-5405-2020-25-1-48-57 EDN: ASICXS

16. Лот 7. ОКР “Разработка и освоение производства радиационно-стойкой отказоустойчивой ПЛИС емкостью не менее 250 тыс. логических вентилей со встроенными блоками PLL и умножителями”, шифр “Алмаз-14”. URL: https://zakupki.gov.ru/epz/order/notice/ok44/view/documents.html?regNumber=017310000951500 0200 (дата обращения: 26.08.2022).

17. ProASIC3 FPGA Fabric User’s Guide URL: https://www.microsemi.com/document-portal/doc_download/130708-proasic-sup-u-plus-u-sup-flash-family-fpgas-datasheet (дата обращения: 26.08.2022).

18. Карпов, С. Flash-семейства ПЛИС “Актел” / С. Карпов // Компоненты и технологии. - 2007. - № 11(76). - С. 5662. EDN: MTFOLD

19. Vassiliadis S., Soudris D. Fine- and Coarse-Grain Reconfigurable Computing. Springer, 2007. 381 с.

20. Karypis G., Kumar V. Parallel multilevel k-way partitioning scheme for irregular graphs // In Proceedings of the 1996 ACM/IEEE conference on Supercomputing (Supercomputing ’96), 1996, IEEE Computer Society, USA, p. 21.

21. Schlag S., et al. k-way Hypergraph Partitioning via n-Level Recursive Bisection URL: https://arxiv.org/abs/1511.03137(дата обращения: 26.08.2022).

22. Donath W. Placement and average interconnection lengths of computer logic // IEEE Transactions on Circuits and Systems, vol. 26, no. 4, pp. 272-277, April 1979,. DOI: 10.1109/TCS.1979.1084635

23. Landman B. S., Russo R. L. On a Pin Versus Block Relationship For Partitions of Logic Graphs // IEEE Transactions on Computers, vol. C-20, no. 12, pp. 14691479, Dec. 1971,. DOI: 10.1109/T-C.1971.223159

24. Иванников, А. Д. Формализация выбора отладочных тестов при проектировании цифровых микроэлектронных систем на основе проверки выполнения требуемых функций / А. Д. Иванников, А. Л. Стемпковский // Известия высших учебных заведений. Электроника. - 2020. - Т. 25. - № 4. - С. 310319. -. DOI: 10.24151/1561-5405-2020-25-4-310-319 EDN: FDJZDF

25. D. Shah, E. Hung, C. Wolf, S. Bazanski, D. Gisselquist and M. Milanovic, “Yosys+nextpnr: An Open Source Framework from Verilog to Bitstream for Commercial FPGAs”, 2019 IEEE 27th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2019, pp. 1-4,. DOI: 10.1109/FCCM.2019.00010

26. Тиунов И.В., Липатов И.А., Железников Д.А. Разработка методов архитектурно-ориентированного ресинтеза в маршруте автоматизированного проектирования ПЛИС. Проблемы разработки перспективных микро- и наноэлектронных систем. 2018. Выпуск I. С. 69-74. DOI: 10.31114/2078-7707-2018-1-69-74

Выпуск

Другие статьи выпуска

В настоящее время большое внимание исследователей привлекает разработка неохлаждаемых ИК матричных микроболометров на базе КНИ структур, что обусловлено их высоким быстродействием и температурной чувствительностью по сравнению с другими болометрическими и термопарными сенсорными элементами, работающими в ИК спектре длин волн. Важным параметром таких КНИ микроболометров является полезная площадь диэлектрической (SiO2) мембраны, поглощающей ИК излучение, и ее хорошая тепловая изоляция, что требует технологического подбора режимов травления жертвенного слоя (Si) через матрицу сквозных отверстий (окон) в SiO2 мембране. В работе проведено TCAD моделирование газофазного травления жертвенного Si слоя с учётом его толщины и размера окон. Показано, что уменьшение размера окон от 120 до 80 мкм2 приводит к снижению в 2 раза времени травления (от 480 до 240 секунд) и обеспечивает эффективное увеличение полезной поверхности чувствительного элемента микроболометра, которая разогревается от ИК излучения. Полученные результаты могут быть полезны в процессе отработки технологических операций изготовления ИК микроболометрических матриц на КНИ подложках.

В статье рассматривается оценка критичности дисперсии ошибок фильтрации фильтра Калмана к изменению коэффициентов фильтрации, которые зависят от шумов маневра и модели маневра. Представлены графики зависимости суммарной ошибки фильтрации от коэффициента фильтрации. Раздельно рассмотрены динамические и флуктуационные ошибки фильтрации.

Выбор метода реализации антенной решетки для допплеровского измерителя скорости и угла сноса обуславливается особенностями режима полета ЛА, его ТТХ и параметрами подстилающей поверхности. Для создания требуемых параметров применяются печатные антенные решетки.

При проектировании энергоэффективных интегральных микросхем на основе современных технологий необходимо использование регуляторов напряжений. Рабочие напряжения, получаемые от доступных альтернативных источников, передаются подсистеме преобразования питания, которая стабилизирует напряжение для нужд потребителей: цифровой логики или СФ-блоков. Данная статья посвящена особенностям использования линейных регуляторов напряжения (LDO). Приведены анализ и результаты разработанного интегрального LDO для самопитаемых систем.

Предложена методика повышения направленности микрополоскового ответвителя путем включения в конструкцию вспомогательной печатной платы, содержащей линии с емкостной связью. Изготовлен макет октавного ответвителя с неравномерностью ±0.5 дБ и направленностью не хуже 23 дБ.

Проводится обсуждение проблем экстракции параметров полосковых структур, связанных с решением комплекса задач использования экспериментальных данных, математических моделей и средств измерения. Рассматриваются алгоритмы восстановления параметров одиночных и связанных полосковых линий на основе экспериментальных данных. Приведены примеры экстракции первичных параметров, фазовых скоростей распространяющихся волн и эффективных диэлектрических проницаемостей. Наряду с использованием данных в частотной области, берутся экспериментальные характеристики отклика на импульсное воздействие. Ставится вопрос о создании приборов для эффективного решения задач экстракции параметров.

Проведены теоретическая оценка и аналитическое моделирование теплофизических параметров термопарных сенсоров с учетом требований по размерам сенсоров, их чувствительности и постоянной времени тепловой релаксации. Определены основные соотношения конструктивных элементов чувствительных ячеек с учетом характеристик технологических слоев, входящих в структуру мембран. Полученные результаты использованы в качестве исходных данных для топологического проектирования сенсорных элементов, и матричных массивов на их основе. Проведено проектирование топологии кристаллов с термопарными сенсорами с учетом возможностей технологического оборудования (нормы проектирования 0,8 мкм).

Приводятся результаты исследований по разработке конструктивно-технологических решений многоэлементных фотоприемных алмазных устройств УФ-диапазона. Приведены результаты применения ионной имплантации бора и азота для формирования заглубленных фоточувствительных слоев. Показано, что полиэнергетическая имплантация больших доз бора позволяет получать слои с высокой проводимостью при комнатной температуре. Полученные экспериментальные зависимости по дозе и энергии ионов демонстрируют возможности создания сильно компенсированных, слаболегированных слоев p-типа и сильнолегированных слоев p+-ram. Показаны конструкция и топология фоточувствительных ячеек на основе ионно-имплантированных слоев матричных алмазных фотоприемников.

Одним из разделов теории цифровой обработки сигналов является теория построения всепропускающих рекурсивных цифровых фильтров, у которых амплитудно-частотная характеристика постоянна на всех частотах, и которые различаются своими фазо-частотными характеристиками. В данной работе предложено распространить разрабатываемый авторами подход к синтезу рекурсивных ЦФ с конечной длиной слова на все пропускающие ЦФ. Подход основан, что нули и полюсы, а значит и коэффициенты передаточной функции, определяются уже с учетом конечной разрядности. Далее производится генерация структур и параметрический синтез, т. е. расчет коэффициентов выбранной структуры. При этом структурный синтез не искажает нули и полюсы. Данная работа ограничена рассмотрением только этапа структурного синтеза и связанного с ним параметрического синтеза.

В статье представлены результаты апробации аналитических моделей для вычисления частотных и временных откликов, учитывающих произвольные оконечные резистивные нагрузки и асимметрию поперечных сечений линий передачи (Л11). Апробация проведена на шести структурах 2-проводной ЛП и трех структурах 4-проводной Л11. Достоверность полученных результатов подтверждена с помощью сравнительного анализа с результатами, полученными с помощью численных методов, который показал согласованность.

В статье рассматриваются аспекты апробации прототипа потокового рекуррентного сигнального процессора на одном из ключевых алгоритмов цифровой обработки сигналов - фильтре с конечной импульсной характеристикой. Первая попытка реализации блочного КИХ-фильтра показала высокий уровень производительности рассматриваемого прототипа. Однако избыточность потоковой программы оказалась слишком высокой. Был осуществлен анализ методов программной и аппаратной оптимизации реализации КИХ-фильтров. По результатам данного анализа определены основные направления для усовершенствования прототипа рекуррентного сигнального процессора. Средства аппаратной поддержки алгоритма Быстрого преобразования Фурье, созданные на более ранних этапах разработки прототипа, были успешно доработаны и использованы для реализации КИХ-фильтра. Данное решение позволило снизить избыточность потоковой программы реализации блочного КИХ-фильтра почти на 80% и повысить скорость загрузки отсчетов обрабатываемого сигнала.

Увеличение быстродействия разрабатываемых устройств - одна из ключевых тенденций развития современной радиотехники. Это ведет к повышению требований и к другим техническим параметрам: помехозащищенности, стабильности, надежности и т. д. Широкополосные усилители являются одним из видов быстродействующих устройств. В свою очередь, к перспективным устройствам широкополосного усиления относят усилитель с распределенным усилением (УРУ), относящийся к классу устройств, работающих по принципу направленного сложения высокочастотных сигналов. В данной статье приведен обзор существующих структур интегральных УРУ, особенность их работы, преимущества и недостатки в сравнении с другими видами широкополосных усилителей. Из-за разнообразия архитектур УРУ требования к технологическому процессу варьируются. Материалы, на базе которых и проектируются усилители, имеют свои плюсы и минусы. В связи с этим, особое внимание было обращено на два популярных технологических процесса используемых в УРУ, а именно GaN и GaAs. Помимо этого, в работе представлена сводная таблица по имеющимся на рынке микросхемам.

Выполнен анализ современного состояния разработок интегральных микросхем (ИМС) для жестких условий эксплуатации, на основании которого предложено использование арсенид-галлиевой технологии HBT-HEMT. Представлены результаты приборно-технологического (TCAD) моделирования электрических характеристик гетеропереходного биполярного транзистора со структурой pnp-типа на основе GaAs. Определены следующие основные параметры: напряжение Эрли Va, коэффициент усиления базового тока в схеме с общим эмиттером BETA, напряжение пробоя промежутка коллекторэмиттер VK3BR, граничная частота /гр. Исследовано влияние на указанные параметры атомарного состава x соединения AlGaAs, ширины активной базы WE и даны рекомендации по выбору их оптимальных значений. Приведена оценка изменения параметров приборной структуры pnp-HBT при вариации температуры.

Рассмотрена математическая модель ячейки цилиндрической формы магнитной памяти произвольного доступа на основе спинового эффекта Холла. В приближении однородного намагничивания построена система дифференциальных уравнений, описывающая динамику намагниченности в свободном ферромагнитном слое ячейки. Проведен ее качественный анализ.

В настоящее время предложены методы повышения надежности SPN-криптосистем, основанные на применение полиноминальной системы классов вычетов. Применение подобных кодов позволяет перенести вычисления из области GF(28) в область GF(24), что положительно отражается на скорости и надежности функционирования вычислительных систем. В данной статье описываются результаты применения подобных технологий в процедурах SubBytes и MixColumns SPN-систем, исследуется эффективность корректирующей способности подобных кодов, оценивается выигрыш относительно классического варианта построения криптосистем.

В статье рассмотрены ограничивающие производительность недостатки микроархитектур популярных 32-разрядных софт-процессоров для встраиваемых систем на основе ПЛИС. Предложена микроархитектура софт-процессора на базе архитектуры RISC-V, лишенная рассмотренных недостатков. Проведена верификация и оценка аппаратных характеристик разработанного софт-процессора. Разработанный софт-процессор имеет на 17% большую производительность по сравнению с рассмотренными решениями.

Описаны характеристики разработанного 32-разрядного микропроцессора с архитектурой набора команд RISC-V. Рассмотрены его основные модули и доступные конфигурации, а также возможные сферы применения данного микропроцессора. Описана конструкция и характеристики тестовой микросхемы на основе разработанного микропроцессора, а также измерено её энергопотребление и падение напряжения на линиях питания при напряжении питания 3,3 В и 5 В. Проведён анализ производительности различных конфигураций микропроцессора. Представлен сравнительный анализ производительности разработанного микропроцессора и его аналогов. Проведён анализ зависимости площади, занимаемой микропроцессором на кристалле от его конфигурации. Сделаны выводы об оптимальности применения определённых конфигураций микропроцессора для решения различных типов задач.

Удаленные лаборатории вызывают растущий интерес у исследователей по всему миру. Такие лаборатории преимущественно создаются для конкретных учебных условий, поэтому невозможно в полной мере использовать стороннюю лабораторию для проведения онлайн-занятий в МИЭМ НИУ ВШЭ, на дисциплинах, где используются ПЛИС (программируемые логические интегральные схемы). Предлагаемое решение представляет собой удаленную лабораторию, состоящую из серверной и клиентской частей, а эксперименты - взаимодействие с платами ПЛИС с возможностью управления кнопками и переключателями, что позволяет максимально приблизить работу в удаленной лаборатории к практическим занятиям по изучению ПЛИС. Результаты экспериментов показывают, что удаленная лаборатория имеет ряд преимуществ перед существующими средствами для проведения практических занятий.

В основе функционирования сверточных нейронных сетей (СНС) лежит операция умножения вектора на матрицу, в связи с чем для построения производительных СНС требуется разработка быстродействующих вычислителей. Один из путей проектирования таких устройств связан с аппаратной реализацией алгоритмов быстрого умножения, в частности алгоритмов умножения на группу разрядов (алгоритмы Бута, Мак-Сорли и др.). Полученные матричные структуры могут быть оптимизированы при разработке топологии с целью минимизации площади кристалла. В статье рассматриваются варианты ускорения работы умножителей с использованием методов умножения на группу разрядов, предложены варианты топологических реализаций рассмотренных решений, позволяющие достичь компромисса между быстродействием и площадью кристалла.

В статье рассматриваются варианты отображения классической программной конструкции «цикл» в потоковую парадигму программирования, реализованную в архитектуре параллельной потоковой вычислительной системы (ППВС). Кратко описаны потоковая модель вычислений с динамически формируемым контекстом и реализующая её архитектура ППВС. Приведены примеры, поясняющие специфику использования вариантов отображения конструкции «цикл». Отдельно описаны методы контроля окончания циклов. Проанализированы преимущества и недостатки описанных вариантов и методов.

Предложена методика по созданию аппаратной реализации ускоренного приближённого матричного умножителя MADDNESS. Данный умножитель имеет хорошие показатели по точности и скорости работы и одновременно отличается простотой декодера, что позволяет его широко применять в аппаратной реализации нейронных сетей. В результате исследований удалось достичь очень высокой скорости работы умножителя на аппаратном уровне за счёт полного отказа от операции умножения как таковой. При этом качество полученных предсказаний остаётся высоким.

Целью исследования является анализ применения имеющихся свободно распространяемых программных инструментов с открытым исходным кодом для полного цикла проектирования цифровых микросхем от HDL описания до геометрии GDSII Результаты сравниваются с результатами коммерческого программного обеспечения Cadence.

Решение задачи оптимизации схемы получено на основе комбинации генетического алгоритма (ГА) и идеи обобщенной оптимизации, разработанной ранее для детерминированного случая. Показано, что такая модификация ГА позволяет преодолеть преждевременную сходимость к локальным минимумам и на несколько порядков повысить точность минимизации. В этом случае ГА формирует множество популяций, определяемых фитнес-функцией, заданной по-разному, в зависимости от стратегии, выбранной в рамках идеи обобщенной оптимизации. Способ задания фитнес-функций, а также длина и структура хромосом определяются искусственно введенным управляющим вектором в рамках обобщенной оптимизации. Этот вектор определяет количество независимых переменных задачи оптимизации и метод вычисления фитнесфункции. Он позволяет строить составные стратегии, значительно повышающие точность получаемого решения. Это, в свою очередь, позволяет уменьшить количество генераций, необходимых при работе ГА, и минимизировать процессорное время на решение задачи оптимизации схемы.

Рассматривается задача верификации реактивных систем управления с параллелизмом поведения. Полагается, что описание функционирования устройства, заданного на языке параллельных автоматов, корректно, проверке подлежит схемная (или программная) реализация. Генерация тестовой последовательности основана на обходе графа достижимых состояний параллельного автомата. Предлагается метод сокращения графа достижимости, который основан на предположении независимости параллельно происходящих переходов автомата. Усечение графа достижимости достигается за счет доопределения частичного порядка на множестве переходов, позволяющего существенно уменьшить число рассматриваемых состояний системы управления и, соответственно, число вершин графа. Получаемое сокращение графа достижимых состояний позволяет решать задачу построения тестов для более сложных систем управления.

В работе приведен разработанный авторами алгоритм автоматизированного визуального контроля монолитных интегральных схем и описываются его модификации для повышения эффективности. Осуществленные модификации заключаются в изменение порядка расчёта карты дефектности, введении расчёта средневзвешенного пиксельного расстояния и в изменении веса слоёв фотошаблона. Проведенное тестирование модификаций на наборах микрофотографий монолитных интегральных схем различных топологий показало, что изменение порядка расчёта карты дефектности и изменение коэффициента веса слоёв фотошаблона позволили существенно повысить повторяемость ручного визуального контроля до 98%.

Растущая сложность современных систем обработки видеоинформации и ограниченные сроки их проектирования требуют применения новых инструментов разработки, используемых в современных системах автоматизированного проектирования и основанные на программируемых логических интегральных схемах (ПЛИС). В настоящее время в дополнение к традиционным языкам описания аппаратного обеспечения (hardware description languages - HDL) всё большую популярность набирают инструменты высокоуровневого синтеза (High Level Synthesis - HLS) микроархитектур, преимущество которых состоит в повышении уровня абстракции при разработке различных систем обработки сигналов, в частности изображений в области транспорта. Несмотря на простоту проектирования и тестирования в сравнении HDL, при использовании HLS необходимо учитывать недостатки, проявляющиеся при генерации описания аппаратного обеспечения, свойственные данному подходу. В статье на примере проектирования известного фильтра Кэнни, позволяющего выделить границы транспортных объектов на изображениях при решении задач обнаружения и распознавания, представлено сравнительное исследование двух методик синтеза цифровых устройств обработки изображений: HLS и HDL. Приведены результаты сравнения двух реализаций HDL и HLS, полученные на основании оценки вычислительных ресурсов и времени выполнения операций. Поскольку фильтр Кэнни, как и многие другие фильтры выделения контуров, является сверточным, данная работа позволяет оценить сильные и слабые стороны любого оператора в области обработки изображений. Исследование показало, что с учетом затрачиваемых ресурсов и времени отклика реализация HLS продемонстрировала более высокие показатели с точки зрения задействования ресурсов и времени отклика в сравнении с подходом HDL.

Современные системы автоматизации проектирования разрабатываются с использованием графических интерфейсов пользователя. Применение таких интерфейсов позволяет упростить и ускорить разработку устройств. В данной работе рассматривается проблема разработки алгоритмов визуализации, необходимых для создания инструмента графического проектирования цифровых интегральных схем на вентильном уровне. Предложена графовая модель представления схемы как основа для разработки алгоритмов. Рассмотрены алгоритмы размещения и трассировки, необходимые для построения графического представления схемы. Упомянутые алгоритмы реализованы в виде программного модуля на основе разработанной графовой модели. Представлены результаты работы программного модуля для некоторых схем из набора ISCAS’89.

Применимость методов машинного обучения для тестирования моделей процессора в настоящее время исследуется в крупнейших иностранных технологических компаниях (исследовательские центры ARM, Intel, IBM и другие) и институтах. Однако исследования проводятся только с точки зрения машинного обучения в области формальной верификации, генерации тестов с использованием символического выполнения и решения ограничений, а также для поиска нерегулярных ошибок в уже изготовленном кристалле СБИС микропроцессора. Новизна предлагаемого решения в применении машинного обучения для имитации поведения приложений пользователя с целью повышения качества тестирования RTL-модели микропроцессора направленными псевдослучайными методами генерации тестов. В рамках данной работы планируется показать применимость инструментов машинного обучения для функциональной верификации RTL-модели микропроцессора на системном уровне. Основным результатом проведенного исследования является возможность имитировать поведение набора пользовательских приложений на уровне машинного кода, а также автоматизация процесса анализа труднодостижимых в рамках классического маршрута верификации ситуаций с целью повышения тестового покрытия.

В статье рассмотрены отечественные и зарубежные технологии аппаратной поддержки вычислений процессоров и анализаторов программного обеспечения как методов снижения уязвимостей памяти. Приведены основные архитектурные отличия таких технологий защиты как Эльбрус, CHERI и Arm MTE. Исследованы существующие статические и динамические программные анализаторы на предмет методологии работы и преимуществ по выявлению дефектов в программном коде.

Рассматриваются хеш-функции, основанные на замещении символов алфавита целыми неотрицательными числами. Основным параметром таких функций является отображение T, осуществляющее замещение; основное назначение функций - выполнение статического хеширования; главные преимущества -высокая скорость работы и простота их реализации. Предлагается алгоритм, выполняющий оптимизацию параметра T с целью уменьшения количества коллизий для заданного словаря. Приводятся примеры эффективных хеш-функций, основанных на замещении символов.

Описан пример синтеза многопроцессорной вычислительной структуры. В основе алгоритмов синтеза лежат сетевые модели и тензорная методология. Описаны основные этапы синтеза вычислительных структур, которые включают декомпозицию исходной модели, вычисление тензора преобразования, формирование программы синтеза новой структуры, а также синтез самой вычислительной структуры. Проанализированы результаты синтеза с точки зрения эффективности загрузки процессорных элементов.

Самосинхронные цифровые схемы имеют ряд преимуществ перед другими типами схем. Для обеспечения этих преимуществ необходимо специальное построение и устройств с памятью, и информационной части схем и индикаторной подсхемы. Одними из главных проблем синтеза самосинхронной схемы являются снижение затрат в транзисторах и улучшение быстродействия информационной части схемы и индикаторной подсхемы. Оба показателя прямо зависят от наличия в библиотеке для синтеза однокаскадных элементов с одним выходом и большим числом входов. Целью работы было найти регулярный способ определения таких элементов. Предлагается формализованный метод выбора библиотечных логических элементов для синтеза самосинхронных схем. Метод позволяет сформировать такой состав библиотеки, который будет давать оптимальные решения при синтезе самосинхронных схем с использованием критериев минимального числа транзисторов и максимального быстродействия.

В данной статье представлен метод трехуровневой логической минимизации. Основой для него послужил алгоритм двухуровневой минимизации Espresso. Ключевое различие состоит в том, что логическая функция представляется в виде суммы произведений литералов и XOR-группы. Такое представление позволяет адаптировать под себя алгоритмы Espresso и сделать их более эффективными. Масштабируемость метода гарантируется за счет сведения его реализации к алгоритмам Espresso, а также использования матричных операций, позволяющих проводить вычисления на графических ускорителях. На данный момент реализованы и протестированы трехуровневые аналоги expand и irredundant. Тестирование проводилось на схемах из набора LGSynth’91. Предметом оценки являлась эффективность алгоритма в сокращении входной логической функции, а также его быстродействие. Для сравнения использовалось программное средство Espresso в аналогичной конфигурации. Результаты экспериментов показывают, что при дальнейшем исследовании темы у трехуровневой оптимизации есть потенциал развития.

В работе предложен подход к построению схем функционального контроля, который заключается в автоматизированной генерации помехоустойчивого кода для каждой конкретной комбинационной схемы. Генерация помехоустойчивого кода основана на кластеризации информационных слов по критерию минимизации вероятности перехода внутри кластера. Под переходом понимается искажение выхода комбинационной схемы. Вероятность такого искажения оценивается путём моделирования схемы при инжектировании однократных ошибок. Такой подход позволяет строить коды, наилучшим образом адаптированные для каждой конкретной комбинационной схемы, достигая максимальных вероятностей исправления ошибок.

Статистика статьи

Статистика просмотров за 2025 - 2026 год.

Издательство

- Издательство

- ИППМ РАН

- Регион

- Россия, Москва

- Почтовый адрес

- 124365 Москва, Зеленоград, ул. Советская, дом 3

- Юр. адрес

- 123182 Россия, Москва, пл. Академика Курчатова, д. 1

- ФИО

- Гаврилов Сергей Витальевич (Директор)

- E-mail адрес

- ippm@ippm.ru

- Контактный телефон

- +7 (499) 7299890

- Сайт

- https://ippm.ru